RVV Intrinsic

RVV向量扩展

使用 Intrinsics 的 C 语言 RISC-V 向量编程

RVV 的灵活性体现在以下几个方面:

- 向量长度的可变性:RVV 提供了灵活的向量长度(VL)设置,使得同一指令可以处理不同数量的数据元素。例如,你可以在同一程序中为不同的操作指定不同的向量长度,以适应硬件的能力或特定的计算任务。一个寄存器可以包含多个数据元素(例如 32 位整数、64 位浮点数等),并根据当前的

vl设置来决定每个寄存器要处理多少数据元素。因此,向量寄存器组有时可以半满或不满——取决于vl设置以及每个操作处理的数据量。 - 向量寄存器组的大小:RISC-V 向量寄存器组通常由多个寄存器组成,每个寄存器的大小是固定的。寄存器的大小和数据类型(如整数或浮点数)是固定的,但由于

vl是动态可调整的,寄存器的填充率可能会小于其最大容量。例如,假设一个寄存器是 128 位宽,如果你只需要处理 64 位的数据元素,寄存器的 “半满” 情况就可能发生。 - 指令和掩码的作用:在 RVV 中,某些指令可以允许掩码操作(例如,

vfmv_v_f_f64m1),这意味着某些元素可能会被忽略或处理为零,而不影响其他寄存器元素的计算。这使得向量寄存器的实际使用情况(如 1/2 或更少)变得有可能。

可行性方案

工具链的安装

1 | git clone https://github.com/riscv-collab/riscv-gnu-toolchain |

程序编写

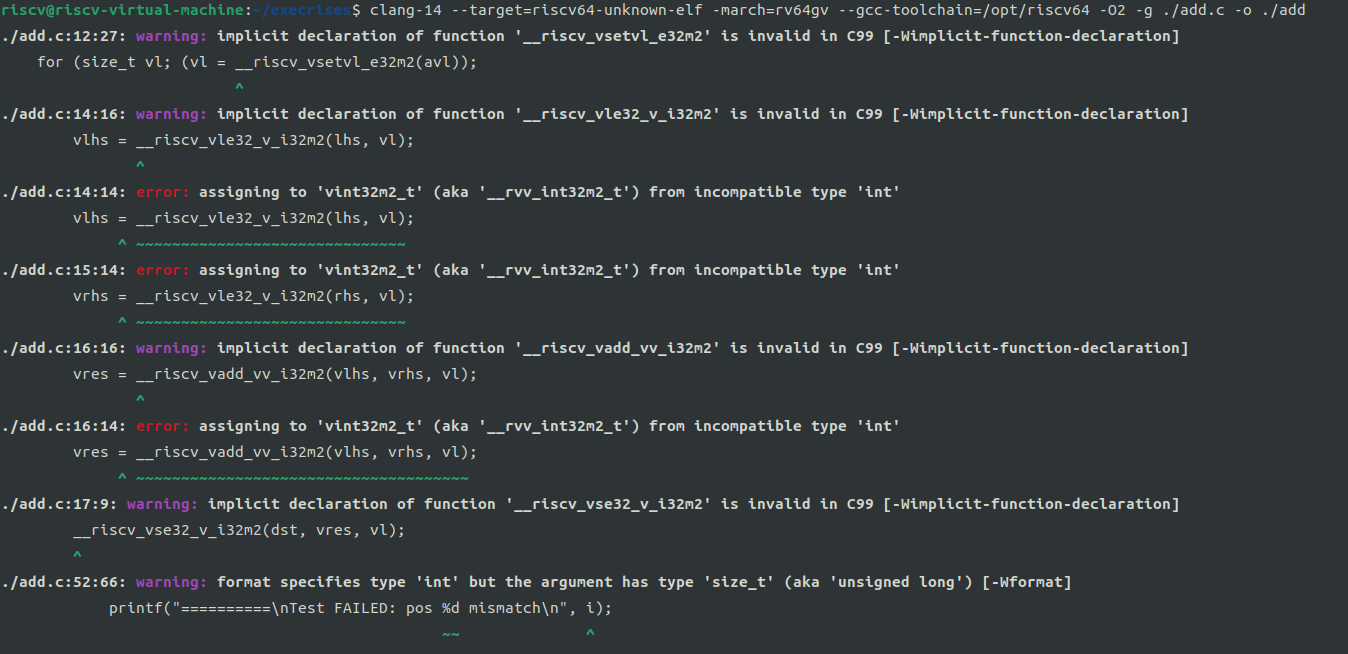

经过测试以上配置的工具版本只能支持具有riscv前缀的函数如__riscv_vle32_v_i32m2(lhs, vl)

更高版本对向量指令的处理方式更严格,因此它不再直接解析某些低级别函数,特别是那些没有前缀的 RVV 内建函数。这种变化旨在减少混淆,并统一 LLVM 中的向量扩展处理。

1 | // Reference: https://pages.dogdog.run/toolchain/riscv_vector_extension.html |

模拟器对于RVV的支持

qemu

1 | ##编译执行报错,说是不支持rvv扩展,所以采用了spike模拟器 |

Spike

安装依赖

在开始之前,你需要确保你的系统上安装了必要的依赖项:

1 | sudo apt-get update |

克隆 Spike 仓库

首先克隆 Spike 仓库到本地:

1 | git clone https://github.com/riscv/riscv-isa-sim.git |

配置和编译 Spike

配置和编译 Spike,使其支持 RVV 扩展。通过以下步骤来完成:

1 | mkdir build |

在这里,--enable-rvv 确保 Spike 配置支持 RISC-V 向量扩展 (RVV)。

配置环境变量

安装完成后,确保将 /opt/riscv/bin 添加到你的 PATH 环境变量中,以便可以方便地调用 Spike。

1 | vi ~./basrch #将一下内容放入最后 |

为了让Spike,正确执行成程序需要将RISCV-V Proxy Kernel(pk)。

安装PK

1 | git clone https://github.com/riscv/riscv-pk.git |

gcc编译

spike只能跑静态编译的程序。

1 | #执行 |

clang编译

1 | clang --target=riscv64-unknown-linux-gnu -O2 -g -march=rv64gcv1p0 -menable-experimental-extensions --gcc-toolchain=/opt/riscv64 --sysroot=/opt/riscv64/sysroot -mllvm --riscv-v-vector-bits-min=256 ./vadd.c -o vadd |

报错

1 | ./vadd.c:10:14: warning: implicit declaration of function '__riscv_vsetvl_e32m1' is invalid in C99 [-Wimplicit-function-declaration] |

等待验证方案

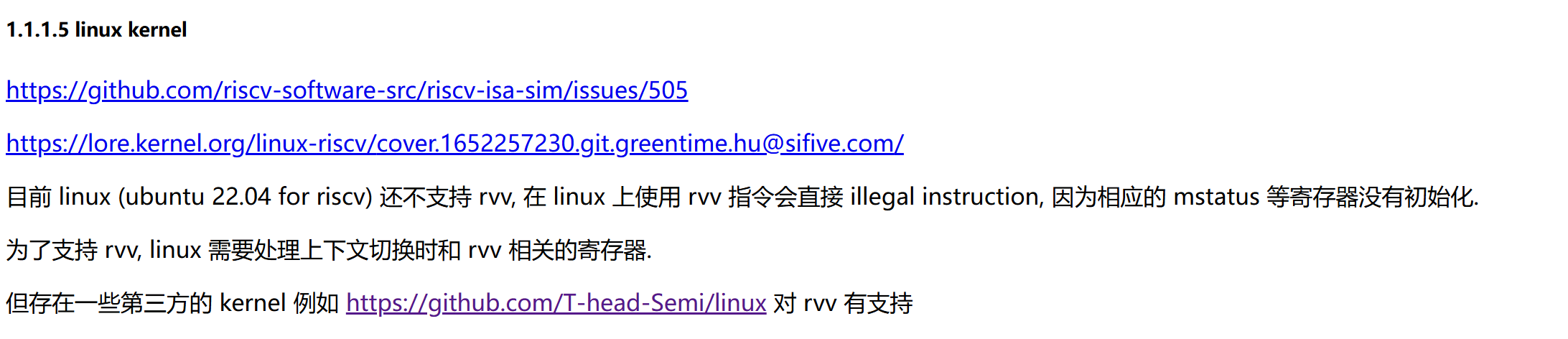

qemu的RVV扩展以及clang为什么编译报错

1 | 使用的qemu是9.0.1的,但是在命令中识别不了vv=true, |

参考链接:[中科院RVV配置Intrinsic](RVV C Intrinsic 配置教程)

参考报告中的工具链版本是13.2,使用的clang是14.0.6,但是我使用的工具链是最新版的14.2.0,这个更高的版本clang14还支持不了,需要更高的版本才可以对RVV的全面支持。

使用clang17是可以编译的。

后续编程实例:

https://github.com/riscv-non-isa/rvv-intrinsic-doc/blob/v0.11.x/examples/rvv_branch.c

函数API为:

qemu关于RVV的编译报错:

在Ubuntu20.04上可以成功运行。